(1)微細2端子・3端子スピントロニクス素子の研究開発

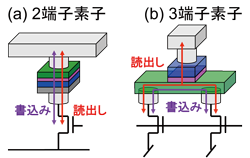

図1 スピントロニクス素子の構造。(a)2 端子素子、(b)3 端子素子。

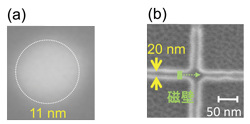

図2 開発したプロセスを用いて作製した(a)2 端子素子と(b)3 端子素子の走査型電子顕微鏡像。

スピントロニクス素子には、図1に示すように2種類の異なる構造のものがあります。2端子素子は、セルのフットプリントが小さく大容量ワーキングメモリ(DRAM等)に適しています。一方、3端子スントロニクス素子は、セルのフットプリントは2端子に比べて大きいものの、書き込みと読み出しの経路を分けることが出来るために、高速ワーキングメモリ(SRAM等)に適しています。微細サイズをする両スピントロニクス素子の研究開発を行うために、2端子素子については直径20nm以下のサイズを有する磁気トンネル接合素子を作製するプロセスを開発し、3端子素子に関しては、線幅20nm以の細線形成プロセスを開発しました(作製した典型的なデバイスの走査型電子顕微鏡像を図2に示しています)。開発したプロセスを用いて、世界最小である直径11nmまでの磁気トンネル接合の特性価と、こちらも世界最小の線幅16nmまでの磁壁移動デバイスの特性評価に成功しています。3端子素子に関しては、プロジェクトの当初目標を既に達成しており、現在は磁壁移動デバイスの高性能化加えて、新しい書き込み方式であるスピン軌道トルクを用いたデバイスに関する研究開発も行っています。また、2端子素子に関しては、図1に示した磁気トンネル接合に直接電流を流して磁化を反転せる方式に加えて、より低消費電力なデバイスとして、電界による磁気異方性の変調を利用したデバイスに関する研究開発も行っています。

(2)耐環境性の評価

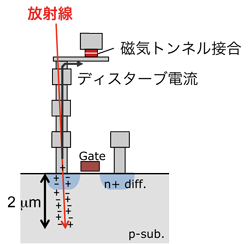

図3 放射線が磁気トンネル接合に与える影響を示した模式図。

半導体ベースのワーキングメモリでは、電荷により情報を記憶するので、放射線の影響により半導体内に電子・正孔対が生成されると、記憶情報の破壊(ソフトエラー)が生じます。この問題は、素の微細化に伴い顕在化します。一方、スピントロニクス素子は、磁化方向で情報を記憶するので、原理的には素子内における放射線に基づくソフトエラーは生じず、微細化しても高い耐放射線耐性が持されます。しかし、図3にも図示しているように、磁気トンネル接合と電気的につながっているCMOS領域において生成された電子・正孔対が磁気トンネル接合に流れ、磁化が反転してしまうことが懸されます。本委託研究では、宇宙航空研究開発機構と共同で、スピントロニクス素子が実際に高い放射線耐性を有するかを検証する実験を進めてきました。直径70nmの磁気トンネル接合に日本原子力究開発機構・高崎量子応用研究所・重イオン照射施設TIARAのマイクロビームを利用して、15MeVのシリコンビームによりシリコンイオンを最大136個まで照射し、照射前後で磁化が反転しないことを証しました。