## 研究スタッフ

教 授: 中島 康治、助教: 小野美 武

## 研究目的

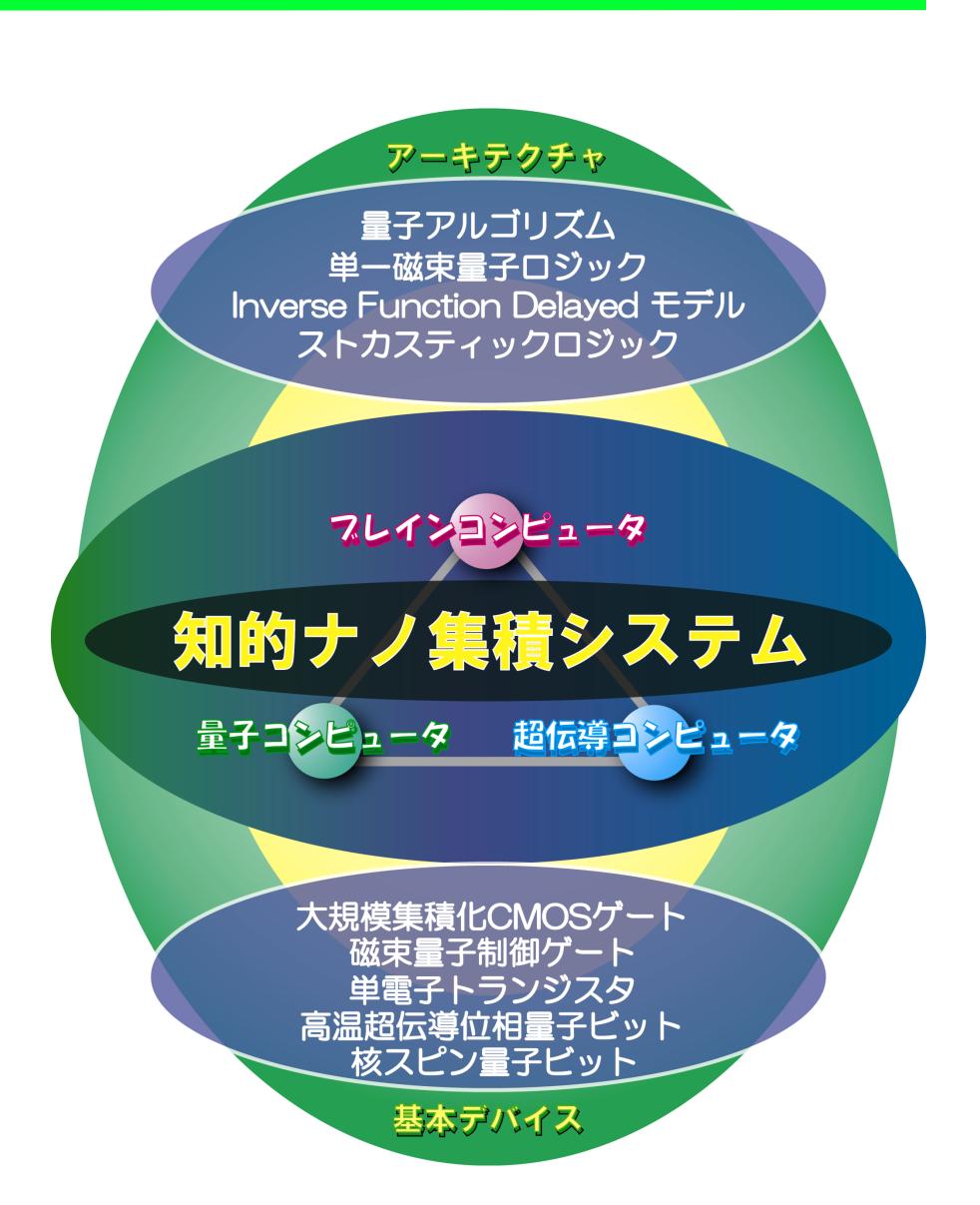

当研究室では、知的情報処理システムの構成法の研究、知的集積回路の設計と製作、人工集積神経回路網の解析と応用、並びにそれに向けた新しいデバイスの開発を行っております。それに伴い大規模集積回路の構成全般にわたる設計・製作・検査から組み立てまでの新概念に基づく基盤技術の開発も合わせて行っております。さらに新たな機能を持つデバイスや知的回路構成法を探索しており、次世代情報処理システムのゲートレベルからの新構築を目指して研究を進めております。

## 主な研究テーマ

## ○ 大規模集債化スレインコンピュータに関する研究

自律分散記憶を核とした知的情報処理システムを構成するため、ニューロシステムへの発振能力の導入による高性能情報処理機能の達成やストカスティックモデルによる高集積化手法の確立などをベースに、超低消費電力、超高速動作のCMOS、単電子、超伝導デバイスを用いた回路設計を行い、連想記憶や最適化処理などを行うブレインコンピュータのマイクロチップ化を目指した研究を行っております。

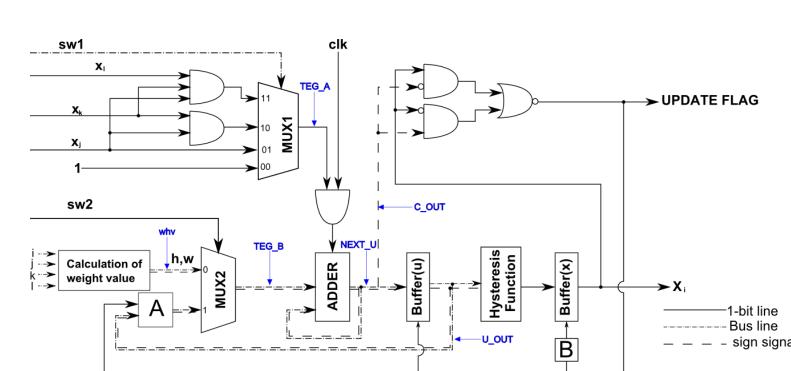

高次結合離散IDニューロンユニット

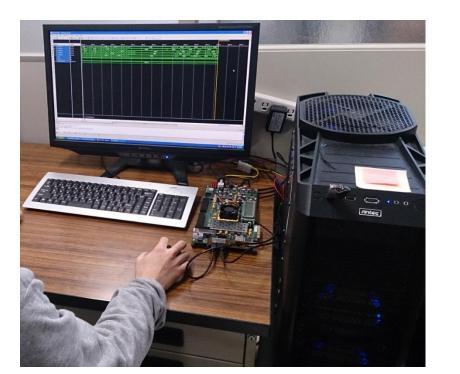

FPGAボードによるニューラルネットワークの実装

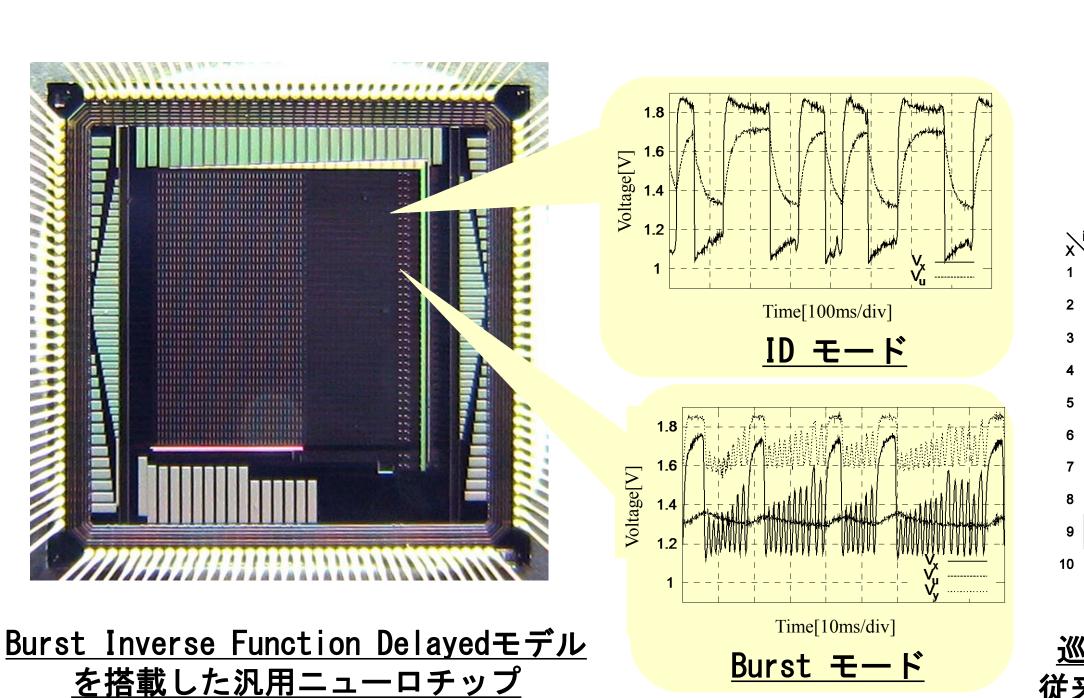

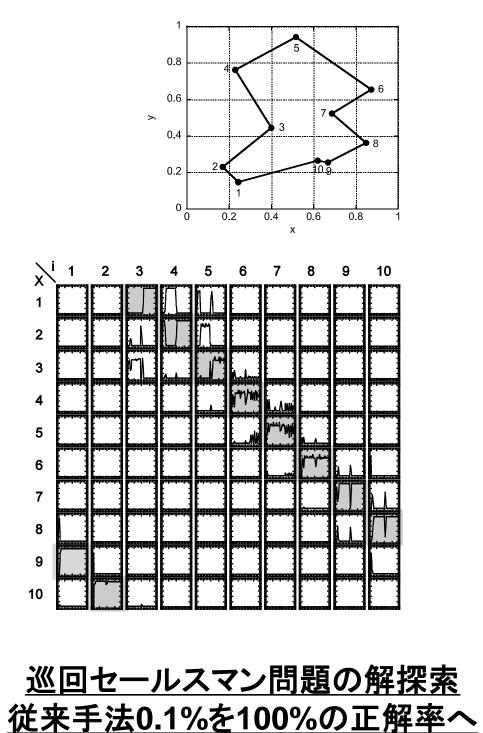

### 高性能最適化処理ニューロチップ(Burstモード搭載)

ActiveニューロンであるInverse Function DelayedモデルにBurst モード(高次ダイナミクス)を搭載した汎用ニューロチップ。コンピュータ並びにこれまでのニューラルネットワークでは困難とされている組み合わせ最適化問題で高い正解率を達成。Burstモードで性能向上を目指す。

#### 汎用ニューロシステム

FPGAボードへ高次結合離散IDニューラルネットワークを実装することにより、ニューラルネットワークの特性である並列処理を実現する。これにより、省スペース・高速・大規模システムが可能となる。モバイルブレインへ向けてのプロトタイプシステムである。

## ンニューロンモデルのアクティス化ビネットワークに関する研究

本研究室では発振能力を持つニューロンモデルとして、逆関数遅延モデル(ID: Inverse function Delayed model)を提案しております。IDモデルによるニューラル ネットワークを最適化問題や連想記憶に適用し、その高性能化を目指した研究を 行っています。

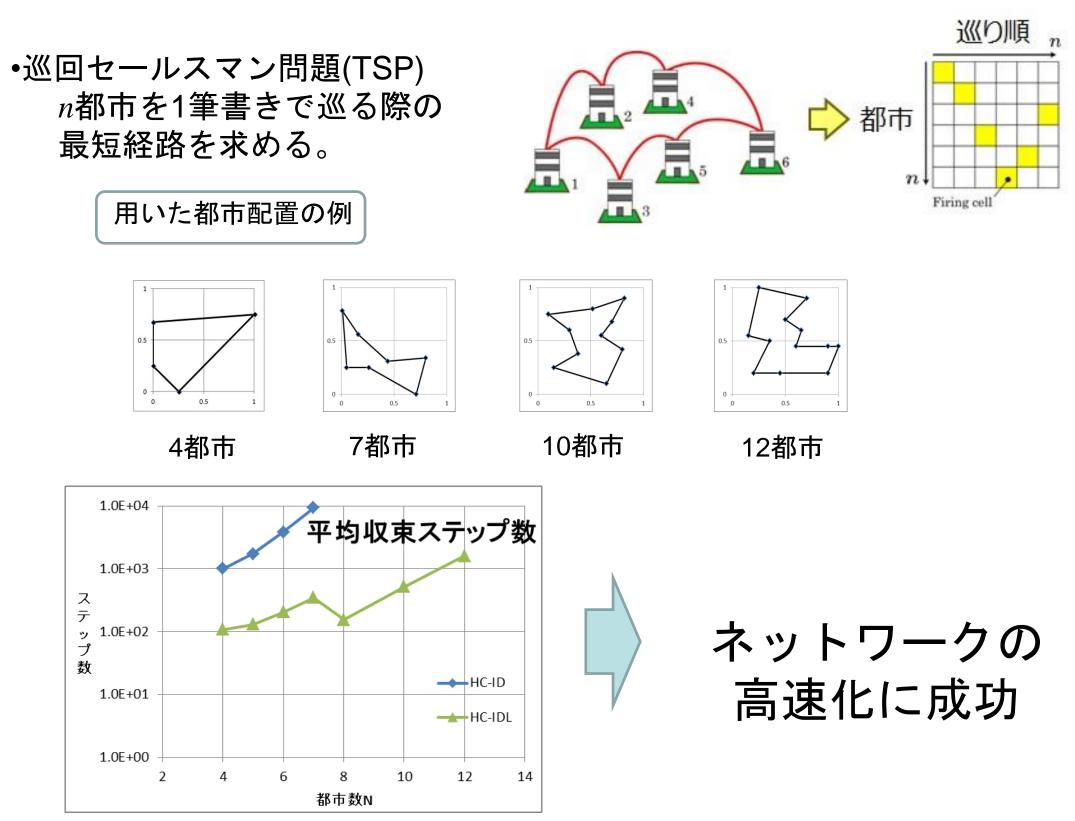

### 逆関数ゼロ遅延モデルによる ニューラルネットワーク

逆関数遅延(ID)モデルの遅延をゼロにし、基 本式を差分化したニューラルネットワークに より、組合せ最適化問題を解くネットワーク の高速化が図られます。

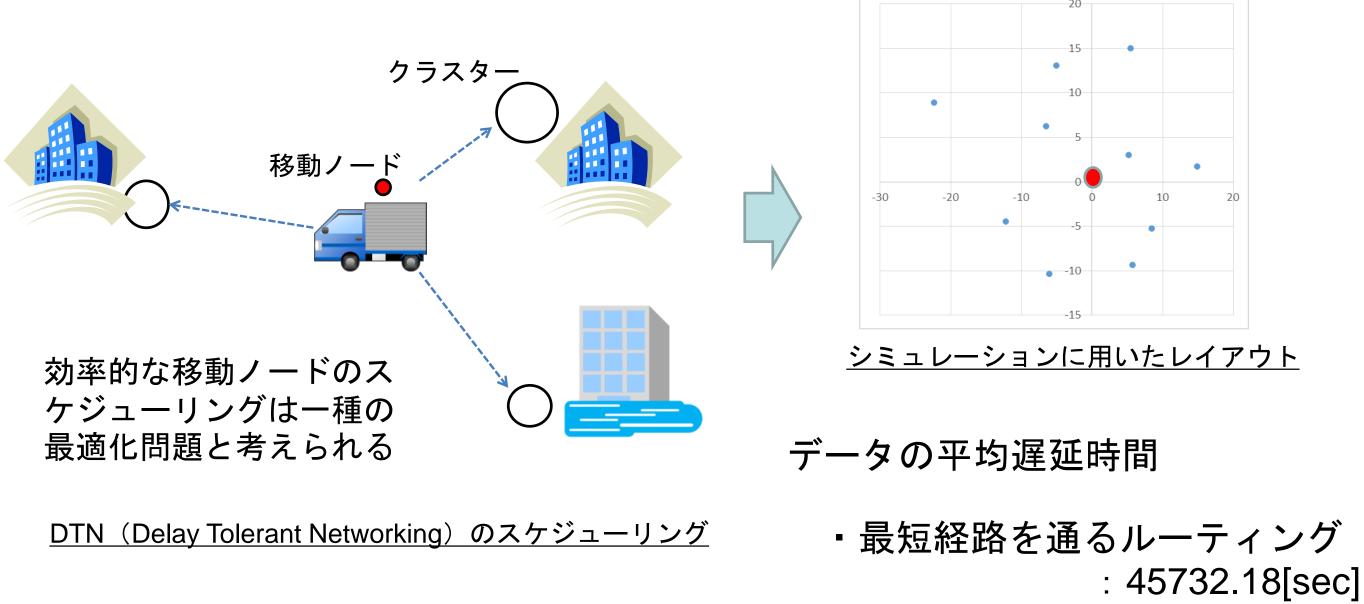

より効率的な移動ノードの スケジューリングを実現

# ニューラルネットワークを用い

た提案手法 : 36643.35[sec]

### 高次結合逆関数遅延ネットワークによるDTNルーティング

DTN (Delay Tolerant Networking)では物理的に移動可能な ノードが孤立したネットワーク(クラスター)で発生したデータを回 収し、他のクラスター、又は生き残った基地局等にデータを配送 する事で通信を行う。効率的な移動ノードのスケジューリングを 行うニューラルネットワークの設計を行っています。

## り置意ローパワー遺伝導コンピュータに関する研究

単一磁束量子を情報担体とした超高速(ps/gate)・低消費電力(μW/gate)の情報処 理回路の研究を行っております。集積化チップはジョセフソントンネル素子を集積 化した回路により試作されます。回路中の磁束量子の挙動や相互作用を論理動作と して利用し、粒子性情報担体としての特徴を生かしたアーキテクチャや設計・集積 化技術の研究を行っております。

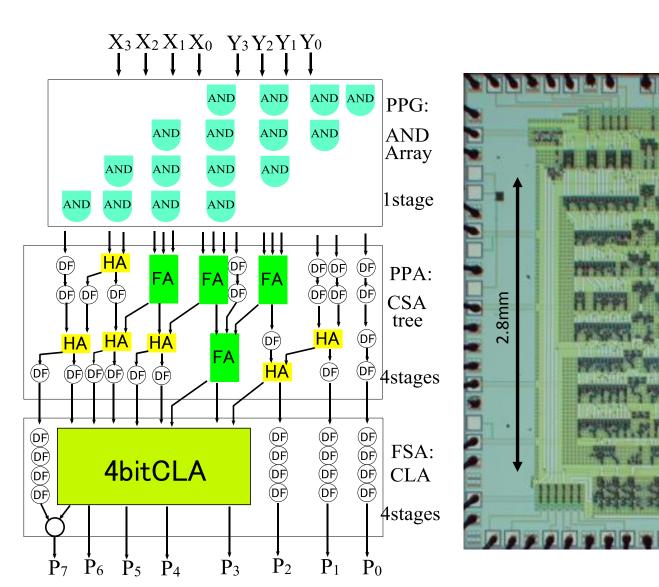

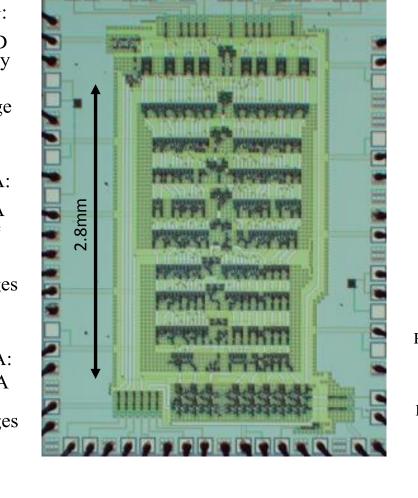

位相モード4ビット並列パイプライン乗算器の構成と集積化回路

(FA:全加算器, HA:半加算器, DF:Dフリップフロップ,

ジョセフソン接合数: 3360個)

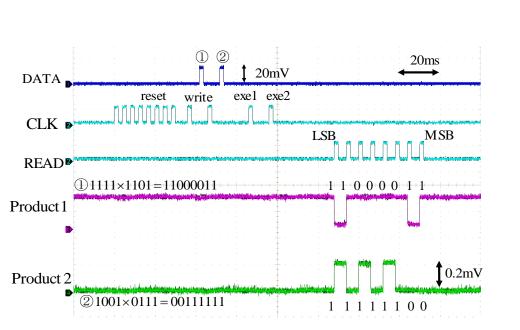

4ビット並列パイプライン乗算器の 論理動作テスト結果

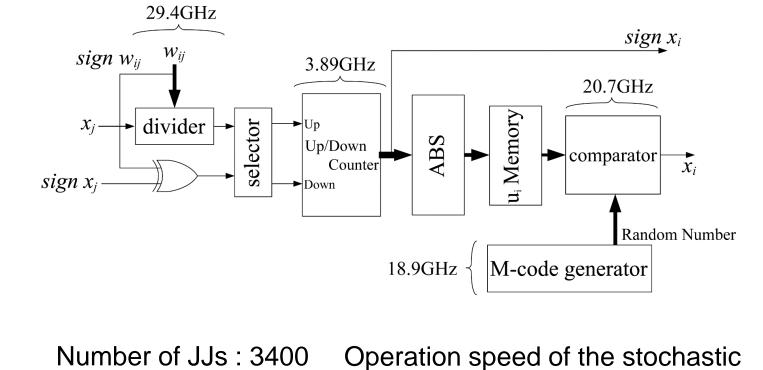

neural circuit (16bit): 3.89GHz

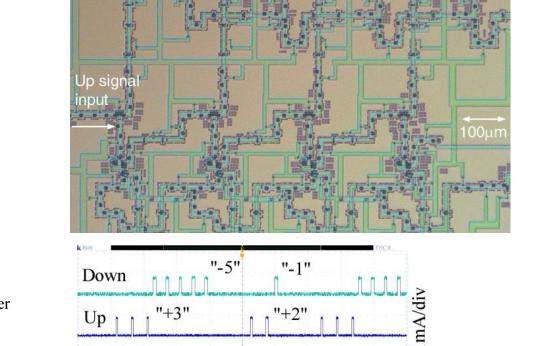

SFQロジックによるストカスティクニューロ回路の構成

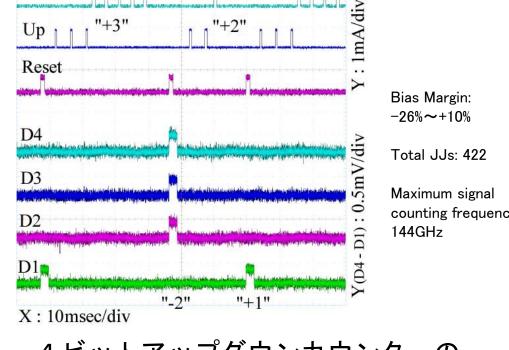

4ビットアップダウン<u>カウンターの</u> 集積化回路と動作テスト

### 位相モード乗算器の集積化

超伝導位相モード方式による超高速・低消費電力プロ セッサの実現を目指して、回路の集積化と検証を行っ ています。図は4ビット並列パイプライン型パラレル乗 算器の回路の製作と測定を示す。回路はNb/AlOx/Nb ジョセフソン接合3360個で構成される。

### ストカスティク論理に基づくニューロ回路の構成

ストカスティック論理に基づくニューロ回路の構成を SFQ回路に適用し、回路構成の提案・数値解析による 評価・集積化回路の試作を通して回路性能の検証を 行っております。