2. 実用的なガロア体算術演算回路の高水準な設計技術の確立を目指して

本プロジェクトでは、これまで培ってきた上記技術を深化・拡張して下記4項目の研究開発を推進します。

(1)ガロア体算術演算回路の形式的設計手法の開発

これまでに開発してきた重み数系に基づく整数算術演算回路の設計手法をもとに、非冗長・冗長ガロア体表現に基づく算術演算回路の形式的表現手法を開発します。整数における各桁の “重み” と各桁の “取り得る値” は、ガロア体ではそれぞれ “基底” と “多項式係数の取り得る値” に対応すると考えられます。これに加えて、ガロア体では既約多項式が演算規則を規定します。以上の観点から、基底の集合、多項式係数の取り得る値の集合、既約多項式によってガロア体を形式的に定義することを考えます。さらに、冗長表現のため、基底集合に任意の冗長性を許す剰余多項式環の基底表現を導入するとともに、既約多項式を既約・生成多項式の積の形で表現する定式化を行います。このように表現されたガロア体を型とする変数を用いて、算術演算回路を有向グラフとして記述する手法を開発します。

(2)ガロア体上の算術演算回路の形式的検証手法の開発

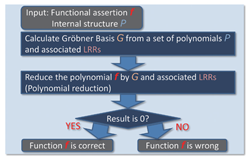

図4 新たに開発する検証手法の概要

上記で開発したガロア体表現により記述されるガロア体算術演算回路の形式的検証手法を開発します。特に、高次のガロア体算術演算を検証するため、これまでのグレブナー基底に基づく形式的検証をガロア体に拡張します。ここで鍵となるのは、冗長表現と非冗長表現を統一的に扱う方法です。冗長表現と擬巡回符号との等価性に着目し、線形再帰関係LRR と呼ばれる関係式を多項式集合に追加してグレブナー基底に変換することで、これを実現しようと考えています(図4)。

(3)暗号プロセッサデータパスの形式的設計・検証への応用

上記で開発した設計・検証手法を実用的な暗号プロセッサに適用します。具体的には、現在世界で最もよく利用されているAES(Advanced Encryption Standard)に基づく認証暗号(AES-GCM)に適用します。ここでは、冗長ガロア体表現による世界最高水準の高速・低消費電力ハードウェアに加えて、各種物理攻撃への耐性を有するセキュアハードウェアの設計と検証を目標としています。

(4)ガロア体算術演算回路ジェネレータの開発と公開

上記で開発した手法で設計・検証されたガロア体算術演算回路を自動生成するジェネレータを開発します。本ジェネレータは、本研究の成果をWeb 上で広く利用してもらうことを目的としており、仕様としてハードウェアアルゴリズム、基数、ガロア体を入力すると、それに応じて機能が完全に保証されたガロア体算術演算回路のHDL 記述を生成するものを目指しています。