- >> 人間・生体情報システム研究部門

-

スピントロニクス・CMOS融合脳型集積システム研究室

教員

[ 教授(兼) ] 遠藤 哲郎

[ 助教(兼) ] 李 涛

研究室HP

https://www.ecei.tohoku.ac.jp/endohlab/index.html

研究活動

電気通信研究所の人間性豊かなコミュニケーション実現の理念とハードウェア関連技術を中心に蓄えた情報通信分野の実績に基づき、材料と情報の基礎科学から、情報を生成・蓄積・認識するためのデバイス、回路、アーキテクチャー、ソフトウェアまでにわたる新分野の開拓を本研究分野の目的とする。

AI時代に求められる情報記憶と情報処理が融合し効率的に動かす半導体集積回路に必要な基盤的研究開発を行う本研究分野を設置することで、情報の量から質の変革をフィジカル空間にて実現する。人間のように高度な情報処理・判断を革新的に効率よく且つ低電力で実行できるハードウェア工学分野を牽引し、発展に大きく貢献することを目指す。

本研究分野は、スピンデバイスの高速と高耐性の特徴を活用することにより消費電力効率を最大化できる次世代AI集積回路アーキテクチャーの提案・設計・検証・評価を一貫して展開し、既存のノイマン型コンピューチィングでは実現が困難な的確な情報価値の決定や取捨選択などの処理をリアルタイムに実装できる新しい脳型コンピューチィングを提供する。

スピントロニクス・CMOS融合脳型集積システム 研究分野|遠藤教授

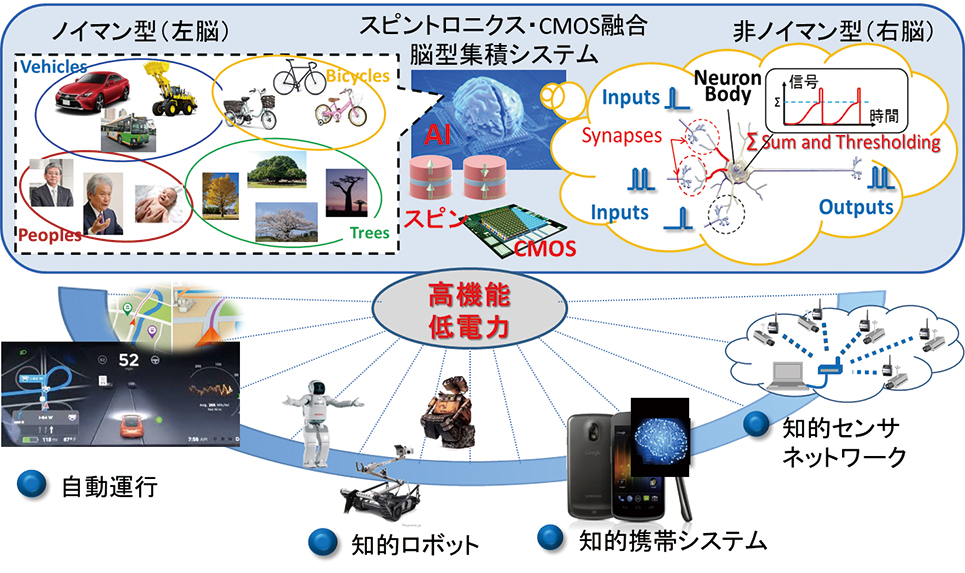

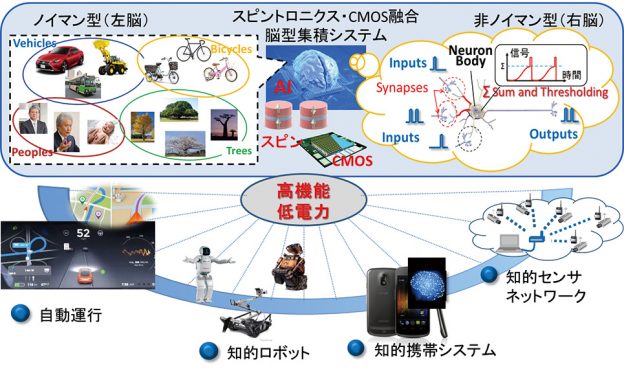

本研究分野においては、スピントロニクス・CMOS融合デバイスに関する理解、スピントロニクス・CMOS融合に基づく回路・アーキテクチャー設計論、脳型CMOS集積回路、及びAIコンピューティング実現のための学理を結集し発展させることによって、スピントロニクス・CMOS融合集積回路の新たな体系を構築し、高機能且つ超低電力のスピントロニクス・CMOS融合脳型集積システムの実現を目的としている(図1)。そのために、研究全体を「ノイマン型」と「非ノイマン型」の2テーマに分け、これらの間での知見の共有、技術の移管、フィードバックを有機的に行っている。

次世代情報化社会における人口知能技術の展開と伴ってヨッタ(1024)バイトを超える超巨大情報が生成されるのみならず、情報の質を加味し人間の思考を支援するAI情報処理をエッジデバイスで行う必要性が増大しつつある。一方、既存の揮発メモリに基づくAI機能を実装するアプローチは、演算あたりのエネルギー効率が非常に悪く、フィジカル空間での適応は困難である。

本研究分野は、「ノイマン型」テーマでは、試作した不揮発適応型K-means教師無学習プロセッサの、オンラインとオフライン学習の精度向上と速度大幅改善を実証するための316PIN BGAパッケージチップをそれぞれ実測評価した。従来の学習方式では対応不能なアンバランス画像データに対して、実測した適応型K-means教師無学習アーキテクチャの精度向上、及び、計算コスト削減を実証できた。更に、図2の示すように、不揮発物体検出認識プロセッサの設計においては、軽量化したFCNNニューラルネットワーク構造を実現する適応型畳み込み演算回路を提案しFPGA検証を行った。加えて、FCNN不揮発物体検出認識プロセッサの55nm - CMOMS / 56nm - MTJ 試作とウェハ測定を完了し課題抽出できた。そして、「非ノイマン型」テーマでは、自律パワー管理技術を導入した32K -Synapse / 512-Neuron構成の8コア / 8レイアSNNパターン認識プロセッサの試作と実測を行い、手書き数字認識における実測機能検証ができ、消費電力評価を完了した。